서론

오늘날 빠르게 변화하고 있는 전세계의 경제 상황은 지속적인 숙련도 향상과 성과 개선을 요구하고 있으며 밀도를 증가시키는 것을 요구한다. 기존에는 추적과 간격을 줄임으로써 밀도를 높여왔다. 그러나 다수의 고속 기판 애플리케이션에서는 더욱 작아진 추적에서 구리와 유전체 손실이 발생하거나 공간 감소로 인해 혼선이 증가하기 때문에 밀도 향상시키는 것이 불가능하다.

기존에 기판 설계와 제작에 사용된 다음의 네 가지 아이디어를 통해, 경로 밀도를 어떻게 높일 수 있는가에 대한 통찰을 얻을 수 있다.

• 랜드리스 바이어스

• BGA 발생을 위한 바이어스 스윙

• 비아-언더-패드를 위한 고체 페이스트 바이어스

• 레이어 밀도 증가를 위한 파워 메시

밀도의 벽 넘기

경로 밀도가 높아진다면, 다음 항목들만이 자유로운 상태가 된다.

• 보다 작은 경로

• 보다 간격이 좁은 추적(공간)

• 보다 작은 바이어스(마이크로 바이어스 단위)

• 바이어스용으로 사용하는 보다 작은 환상 링

• 전송 시 보다 높은 레이아웃 효율 (2016년 6월 29일 뉴스레터 #10-DFM/A에서 정의)

단일 레이어에서의 전송 밀도에 대해 이야기하고 있는 것이다. 보다 많은 신호 레이어의 경우 기판에 있는 전체 전송 길이가 늘어날 것이다.

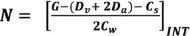

전송 경로에 관한 식은 다음과 같다.

식 1

여기에서, 각 기호는 다음을 의미한다.

N = 채널 내 경로 수

G = 채널 제원 전송

Dv = 바이어스 지름(FHS)

Da = 바이어스의 환상 링

Cs = 도체 간격

Cw = 도체 폭

이 식에서 몇 가지 변수를 소거하는 경우(식 1), 그 결과로 나오는 전송 밀도는 표 1에 나와 있는 비율까지 상승하게 된다. 밀도에 미치는 가장 큰 영향은 경로 폭을 줄이는 것이지만 이는 전기적인 문제를 유발할 수 있다. 차선책으로 바이어스의 환상 링을 줄이는 방법이 있지만, 아주 작은 AR이 바이어스의 신뢰성을 유의미하게 감소시킬 것이다. 따라서 랜드리스는 경로 폭이나 간격을 줄인 상태에서 보다 높은 밀도를 확보할 수 있는 좋은 방법이다.

▲ 표 1. 한 레이어에서 경로 밀도에 PCB 설계가 미치는 영향

다중 레이어 블록에 있는 구멍으로 인해 다수의 경로가 보드 전체를 채널링하기 때문에 블라인드 및 매립 바이어스를 사용하게 되면 사용하지 않은 경우와 비교할 때 레이어 경로 밀도를 두 배에서 최대 네 배 정도 유의미하게 높일 수 있다. 이는 또한 단일 레이어 레이아웃 효율(layout efficiency, L.E.)에 있는 전체 면적과 비교할 때 경로에 사용하는 공간의 크기인 L.E.로 측정이 가능하며, 블라인드 및 매립 바이어스를 사용하는 경우 2배에서 4배 정도 증가한다. TH 다중 레이어에 대한 L.E.는 8 - 10%이다. TH와 블라인드가 있는 바이어스의 경우 16%, TH와 2면 블라인드 바이어스 및 다중으로 구성된 레이어가 있는 경우 최대 24%이다. 표 1에는 바이어스 지름, 환상 링(랜드리스 포함)에 대한 함수로서 다양한 경로 채널 폭에 사용할 수 있는 최대 경로 수를 포함해 증가된 밀도에 기여한 몇 가지 내용이 나와 있다.

랜드리스 바이어스

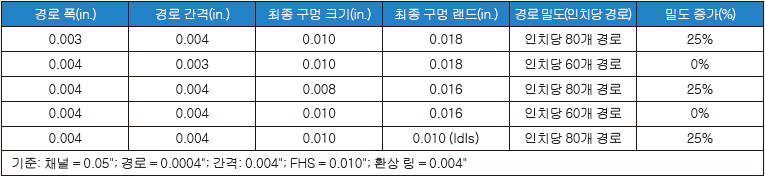

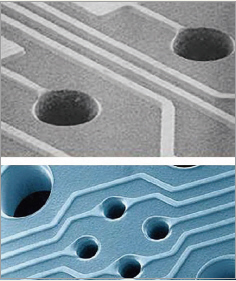

1985년에 일본 토야마의 NEC를 방문하던 중 랜드리스 바이어스 다중 레이어를 처음으로 만나게 되었다[1]. 엄청난 수준으로 자동화가 된 곳에서 일본 통신 및 메인프레임 컴퓨터 기판을 제작했으며 이는 IBM과 Western Electric의 제품을 하나로 통합한 듯한 느낌을 주었다. NEC는 패널 플레이팅을 사용한 포지티브 작동 방식의 포토레지스트 공정인 액체 전기 영동법을 사용하고 있었다. 1988년 일본 협력사인 OKI가 랜드리스 바이어스 다중 레이어를 도입할 때까지는 랜드리스 바이어스 다중 레이어를 볼 수 없었다. OKI는 랜드리스 바이어스를 사용하여 보다 정밀한 라인 구축을 위해 추가 비용을 들이지 않고 밀도를 높였다. 신뢰성이 높아지면 어떻게 되는지 알고 있었다. 자체적으로 실험을 수행하였지만(그림 1) 보다 높은 경로 밀도를 확보하게 되었다. 이러한 바이어스가 그림 2에 나와 있으며, 이를 통해 0.100 인치의 PTH 중심부 사이에 다섯 개의 경로를 설정할 수 있었다.

▲ 그림 1. 랜드리스 바이어스 제작 공정에서 NEC로부터 확보한 신뢰성 있는 데이터[1]

랜드리스 바이어스 프로세스

랜드리스 바이어스와 관련된 특허 어플리케이션들이 다수 등록되어 있다. 이 모든 특허는 바이어스의 제작 또는 정밀 레이저 노출을 사용한 이미지를 필요로 한다. 아직 생산 단계에 들어가지는 못했다. 대량 생산에 사용하는 두 가지 기술과 상당히 실용적으로 판단되는 두 가지 추가 기법을 함께 설명하고자 한다.

일본에서 배운 HP 프로세스

랜드리스 바이어스 제작을 위한 일본의 공정은 상당히 단순하나 프로세스에 대해 설명할 때까지 그 누구도 어떤 식으로 이뤄지는지 이해하지 못했다. 고정관념을 깬 사고를 보여주는 좋은 예이다.

▲ 그림 2. 1985년 무렵 일본의 다중 레이어에

설치한 일반적인 랜드리스 바이어스[1]

1. 등록 공차에 상관 없이, 건식 필름형 포토레지스트를 사용할 때 해당 크기만큼 개방 사이즈를 감소시킨다 그렇게 되면 건식 필름은 구멍의 벽보다 크게 확장된다.

2. 이 작업을 하게 되면 두 가지가 발생한다. 1) 도금조가 구멍으로 힘을 가하기 때문에 분포가 개선된다. 2) 구멍으로 들어간 경로를 제외하고는 랜드가 더 이상 없게 된다.

3. 벗겨내고 식각을 하게 되면, PTH 배럴이나 블라인드 바이어스로 들어가는 경로가 있는 랜드리스 바이어스가 생성된다.

4. 패널 플레이트에 대해서 이 공정을 사용하지 않는다; 해당 공정은 NEC와 같은 차후 공정을 사용해야 한다.

양의 액체 전기영동 포토레지스트

앞서 말했듯, 해당 공정을 1985년 NEC에서 처음 봤다. Nippon Paint에서 양의 전기영동 포토레지스트를 사용하고 있었는데 이는 자동차에서 사용한 전기영동 도료에서 발전한 제품이었다. 미국과 유럽에서는 Shipely가 개발한 보다 작은 포토레지스트를 사용할 수 있었다[2,3]. 보다 최근에 개발된 포토레지스트와 프로세스는 PPG Industries에서 개발했으며 Patricia Goldman(당시 PPG 근무와 Compunetics의 Tim Schmidt가 논문으로 제시하였다[4]. 양에서 작동하는 포토레지스트는 상당히 유용학 사용할 수 있는 다수의 성질을 갖고 있다. 가장 유용한 성질은 다중 노출과 현상, 특히 Ni-AU와 식각에 대한 저항, 정교한 해상도[10마이크론까지 (0.4mil)], 그리고 먼지와 클린룸 파편에 대해 둔감하다는 점 등이 있다. 코팅 과정은 상대적으로 단순하다.

▲ 그림 3. 경로폭과 동일한 지름으로 공급하는 랜드리스 바이어스이며, 이 경우 0.004"임(0.1mm).

'보이지 않는 바이어스'라고 함(출처: HP Sunnyvale PC)

• 패널 청소

• 60 - 100V에서 60 - 90초간 코팅(전압이 최종 두께를 결정한다)

• 세척

• 건조 패널 굽기

이제 패널을 노출시키거나 운송해도 된다. 플레이팅, 노출, 현상, 식각(蝕刻)을 마친 패널 완성품이 그림 4에 나와 있다.

▲ 그림 4. 액체, 전기영동, PPG로부터 양의 포토

레지스트로 생성된 랜드리스 비아(0.010i n

(0.25mm)과 0.004in(0.1mm) 경로](출처:Compunetics Inc.)

완벽한 등록

이제 직접 디지털 이미징(direct digital imaging, DDI)와 보드 스캐닝을 미리 실시한 상태에서 보드 양면에 대해 완벽한 등록을 실시할 수 있다. 양쪽에서 기계로 들어갈 때 패널을 스캔하는 9개 카메라가 달린 DDI 장치가 있다. 그리고, 각 면의 노출을 시작하면서, 제품을 가공간 개조하기 때문에 각 랜드를 구멍에 완벽히 등록하게 된다. 고성능 컴퓨터, 스캐너 및 새로운 소프트웨어가 없다면 불가능했을 것이다.

러시아의 새로운 기법

최근 개최된 PCB West 회의에서 러시아의 PCB 제조업체와 이야기할 기회가 있었다. 러시아 또한 일본의 컴퓨터에서 이를 본 후 랜드리스 바이어스를 사용하는 것처럼 보였다. 러시아의 공정은 상당히 참신했다. 이걸 내가 생각해냈어야 하는데! 이들은 산소에 민감한 필름 포토레지스터의 성질을 사용하였다. 건식 필름을 패널에 부착할 때, 산소를 채운 장치 주변에 막을 씌웠다. 이로 인해 산소는 건식 필름을 통해 구멍에 갇히게 된다. 패널을 일반적인 도판과 함께 노출시켰다(그러나 랜드리스 바이어스와 연결될 경로에 대한 랜드는 없다). 그리고 패널을 100°C로 짧게 구운 후 건식 필름에 있는 커버 시트를 제거한 후 보통과 같이 현상시켰다. 산소와 열이 구멍의 지름과 정확히 같은 지름으로 내부로부터 건식 필름을 중합화시켰다. 그러므로 현상 시, 바이어스는 완벽한 건식 필름 등록이 이뤄지며 랜드리스가 된다.

랜드리스 바이어스가 작은 환상 링이 있는 바이어스에 비해 어떻게 신뢰성이 더 높은지를 포함한 보다 자세한 사항은 최근에 간행된 기사인 ‘Against the Density Wall: Landless Vias Might be the Answer[5]’에서 확인할 수 있다.

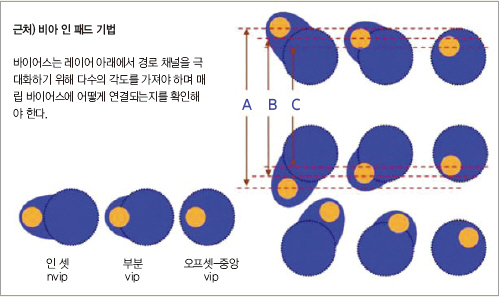

BGA 발생을 위한 스윙 바이어스

HDI에서 확인한 새로운 개념은 일반적인 북-동-남-서 방향으로 회전하는 블라인드 바이어스 정렬이 아닌 동일 채널로 움직여 충격을 주는 방식이다. 이러한 정렬은 장치 피치보다 네 배 더 긴 매장된 바이어스 사이에 폭이 큰 경로를 형성한다. 이 폭은 네 배 넓으며 전역 경로를 위한 막대한 자유 경로를 허용할 수 있다. 이러한 ‘스윙’ 개념은 2011년 저자가 Charles Pfeil과 함께 쓴 기사에 다음과 같이 설명되어 있다.

“바이어스를 경로 생성을 위한 내부 레이어에 있는 넓은 간격을 구성하는 볼 패드에서 떨어진 곳에 ‘스윙’시키는 게 원칙이다. 마이크로 바이어스의 크기, 핀-피치와 볼 패드의 크기에 따라, 마이크로 바이어스를 열과 행에 맞춰 정렬시킬 수 있다. 이를 통해 경로 작성에 가용한 공간이 극대화된다.”[6]

바이어스 구조 통해 개선된 통로

3차원 바이어스 구조를 통해 통로를 개선할 수 있다. 다양한 깊이의 블라인드 바이어스를 사용하면 더 넓은 경로를 형성하는데 도움이 된다. 이러한 구조는 스킵 바이어스, 다중 구성 또는 차후 적층이 된 구멍이 뚫리고 적층된 바이어스를 사용해 생성 가능하다. 또한 원하는 바이어스 구조가 되는데 그 이유는 소형의 인덕턴스가 낮은 블라인드 바이어스를 수평에서 수직으로 변환만 하면 고속의 임계 네트 경로를 제공할 수 있기 때문이다. 기판 내에서 가장 낮은 인덕턴스를 갖는 바이어스가 되며 최고속 네트에 이상적이다. 또한 아주 높은 밀도를 갖게 되는데 그 이유는 교차가 크기가 더 큰 매립 또는 구멍을 통과하는 바이어스가 아닌 작은 블라인드 바이어스가 되기 때문이다.

바이어스 배치 통해 생성되는 통로

Mentor Graphics에서 BGA에 사용하는 여러 형태의 팬아웃 패턴 적용에 있어 새로운 개념을 개발하였다[7]. 표준형 4분면 통신을 사용하는 대신 (북-남-동-서) BGA를 안팎 네 개 영역으로 분할한다. 등록이 향상되고 보다 작은 크기의 환상 링이 있는, 크기가 더 작아진 블라인드 바이어스를 ‘회전시켜’ 경로 채널을 형성한다. 그림 5에 BGA 블라인드 바이어스 위치에 대한 예가 나와 있다.

▲ 그림 5. 바이어스 ‘회전’을 통해, SMT 랜드를 기준으로 비아가 어디에 있는지에 따라 A, B, C 채널

이 생성됨. 이러한 채널은 2, 3배 더 큰 경로 밀도를 갖는 경로임[7].

이러한 개념은 개발자인 Charles Pfeil이 다음과 같이 설명한다.

제 1구역은 외부 열로 구성된다. 열의 개수는 설계 규칙에 따라 4 - 6으로 다르게 나타난다. 이 영역에서는 1:2 마이크로 바이어스를 사용하여 최대 경로 밀도에서 레이어 2에 경로를 생성한다. 이러한 패턴은 바이어스를 볼 패드 근처로 옮기고 각도를 바꾸면 변할 수 있기 때문에 바이어스의 간격이 최소 간격을 초과하게 된다. 이렇게 하면 경로 밀도가 줄어들게 된다; 그러나 평면 공간을 늘릴 수 있기 때문에 바이어스 사이의 잠재적인 크로스 토크가 감소하게 된다.

제 2구역은 모든 내부 열을 포함한다. BGA 핀의 외부 열을 1:2 마이크로 바이어스를 사용해 경로를 설정하는 경우, 다음에 있는 4 - 6열은 1:3 스킵 바이어스를 사용해야 하며, 그 목적은 최대 경로 밀도에서 레이어 3의 경로를 설정하기 위함이다. 스킵 바이어스를 사용하는 경우 레이어 1에서 레이어 3으로 레이어 2에 있는 패드를 사용하지 않고 연결할 수 있다. 이러한 패턴 또한 바이어스를 볼 패드 근처로 옮기고 각도를 변경하면 변화하기 때문에 바이어스 간격이 최소값을 초과하게 된다.

제 3구역은 내부 열 (제 2구역)과 중앙 열 (제 4구역) 사이의 전이 지역이다. 일반적으로 제 2구역과 제 4구역 사이의 패턴이 충돌하여 DRC 위반을 초래하기 때문에 전이 지역이 필요하다. 1:2 또는 1:3 바이어스를 전이 지역에 사용할 수 있으며 이는 경로 설정 전략에 따라 상이하다.

이 예에서, 패턴은 단순한 직교형의 짧은 dog-bone이다. 사용하는 바이어스의 크기에 따라 다른 각도를 사용할 수 있다.

제 4구역은 중앙이다. 가운데 열은 다른 구역을 정의한 후 남은 열이다. 일반적으로, BGA의 중심에는 파워 및 그라운드 핀이 있기 때문에 표준 dog-bone 패턴에서 바이어스를 통해 배치가 이뤄진다. 바이어스가 볼 패드 매트릭스의 정중앙에 위치하지 않는다는 사실을 기억한다. 이를 통해 레이어 1에서 보다 큰 그라운드 평면을 채울 수 있다.

직교 지역 (1). 직교방향으로 나열한 핀은 제 1구역과 2구역의 팬아웃이 합해질 때 충돌이 일어날 수 있다. 그림 5에 있는 예는 패턴의 병합은 물론, 중앙선을 기준으로 떨어진 바이어스를 보여주며, 직교방향으로 보다 큰 경로를 제공하고 있는 모습을 보여준다.

BGA를 구역별로 분할하게 되면 최대 경로 밀도를 얻을 수 있기 때문에 필요한 레이어 수를 줄일 수 있다. BGA에 1,500개 이상의 핀이 있을 때, 단순히 BGA 외부로 경로를 설정하게 되면 레이어 개수 증가에 큰 기여를 하는 경향이 있다. 스택 및 가용한 바이어스 간격에 따라 각 구역별로 사용하는 열의 개수를 변화시킴으로써 고유의 설계 맥락에서 최적의 팬아웃과 경로를 확보할 수 있다.”[7]

이렇게 이동한 블라인드 바이어스를 사용해 정렬한 바이어스 패턴은 대형 BGA로부터의 분열을 유의미하게 증가시킨다. 그러나 다른 장점도 갖고 있다.

• 바이어스 전체와 이동하지 않은 블라인드 바이어스에 대해 경로 밀도가 24% 증가

• 마운트 레이어에 있는 그라운드 평면에 더 많은 공간을 제공 (그러나 패드 내 바이어스 정도의 공간은 아님)

• 블라인드 바이어스를 사용해 레이어에서 고속의 단일 엔드 네트를 경로를 구성하는 경우, 바이어스 스텁이 사라지면 바이어스 대 바이어스 크로스토크가 최소화된다.

• 블라인드 바이어스 레이어에서의 신호 경로가 매립 바이어스를 가질 필요가 없기 때문에 매립된 바이어스 레이어에서도 경로 공간을 구성할 수 있다.

• 블라인드 및 매립 바이어스 스택이 바이어스를 관통하는 스택에 비해 비용이 약간 높다는 단점이 있다.

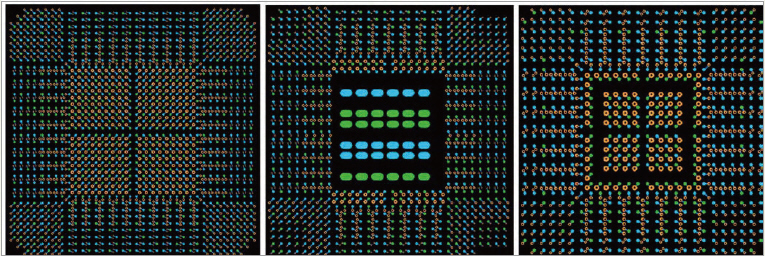

이동 블라인드 바이어스의 예

이동-정렬 바이어스 패턴에 관한 좋은 예는 1,760개의 핀이 있는 Virtex-4와 Virtex-5 FF1760 시리즈 FPGA와 Pfeil의 논문에 나온 1mm 핀치가 있다[5]. Xilinx Application Data 시트는 장치 분해를 위해 6개의 신호 레이어를 어떻게 사용하는가를 보여준다. Pfeil의 논문에서, 이동정렬된 바이어스 패턴을 사용해 경로를 구성하는 방식으로 두 개의 신호 레이어만을 사용해 브레이크아웃을 완성하였다. 또한 그림 6에 스택업에 관한 내용이 나와 있으며 이는 공통적으로 사용하고 경제적인 IPC Type II 12-layer HDI이다.

▲ 그림 6. Virtex 5, 1,760 pin FPGA의 예. '스윙 바이어스'를 사용한 세 가지 대체 표면 발생[7]

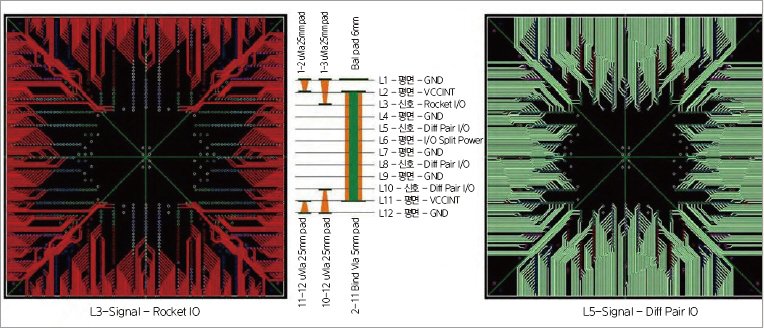

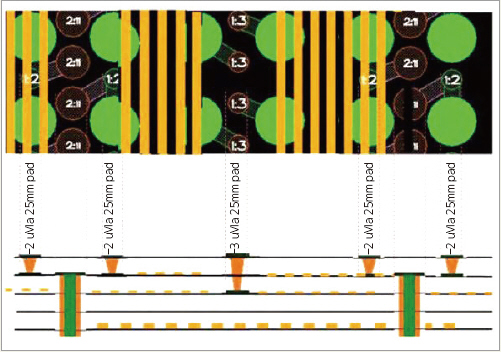

이를 어떻게 완성하는가를 이해하기 위해선 HDI 스택업과 정렬-변경된 블라인드 바이어스를 면멸히 관찰해야 한다. 그림 7에서 보다 자세한 사항을 확인할 수 있다. FPGA 핀 2개 열을 레이어 3으로 팬 아웃시키고 (50옴의 싱글 엔드 Rocket I/O에 대해 스킵 바이어스를 사용 다음 두 개 열을 레이어 2에 팬 아웃시킨 후 레이어 5에 있는 매립 바이어스로 떨어뜨린다(100옴 차등 페어 I/O). 이러한 배열을 통해 매립 바이어스간 통로가 장비 피치보다 네 배 커지게 된다. 이 통로의 폭은 4.0mm이며 최대 13개 경로 구성이 가능하게 된다 - 전역 경로 구성에 있어 상당히 큰 자유 경로가 된다. 레이어 5를 사용하면, BGA는 대규모 경로에 대해 바이어스로 정렬된 경로를 생성하는 매립 바이어스만 있기 때문에 사라진다.

▲ 그림 7. 스택업 관점에서 Virtex 5, 1760 pin FPGA, 레이어 3 및 5 발생 경로에 관한 예

고체 페이스트 바이어스

이 장은 시간이 지나면서 발전하는 다양한 고급형 HDI 제작 공정 검토를 목표로 한다. 상호 연결된 비아 홀(interconnect via hole, IVH) 구성은 HDI 배선 기판 제작에 있어 단순히 한 가지 방법이지만 레이저 천공 기술은 IVH가 기반을 잡은 기타 다수의 방법을 정의함에 있어 가장 널리 사용되는 방식이라는 사실을 인지해야 한다. 다른 두 가지 중요한 요소는 다양한 유전체 물질과 금속화 기법이다. 마이크로 바이어스 구멍이 있는 HDI 배선 기판의 제작을 위해선 기존의 기판 제작과 공통되지 않은 다수의 새로운 공정을 필요로 한다. 따라서 기타 마이크로 바이어스 기술과 공통된 새로운 제작 공정에도 관심을 가져야 한다.

▲ 그림 8. 그림 7의 Virtex 5 발생 클로즈업[7]

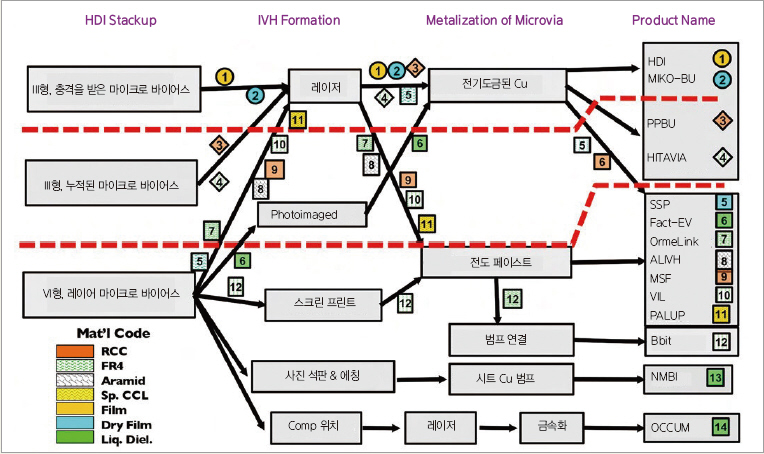

HDI 공정 요소의 정의

그림 9에 현재 사용되는 HDI 기술을 구성하는 네 가지 요소가 나와 있다: 비아 스택업, 유전체, IVH 구성 물질, 그리고 z-축 비아 연결의 금속화 기법에 관한 부분이다. 최근 몇 년간, 14가지의 여러 고급 HDI 공정을 활용하였다.

▲ 그림 9. 현재 사용하고 있는 HDI 기법은 네 가지 주요 요소로 이뤄지며 이는 마이크로 비아 스택업 아키텍처, 유전체 물질,

IVH 정보 기법 및 z-축 비아 연결에 대한 금속화 기법이다. 최근 몇 년간, 14 가지의 HDI 공정을 개발하였다.[8]

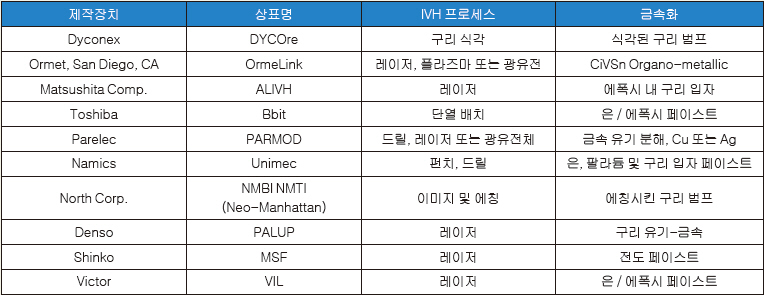

고체 전도 비아 충진

HDI 기술의 IPC 형식 VI 그룹은 모두 금속 페이스트나 고체 금속 시트를 사용하여 비아 연결을 구성한다. 표 2에 IVH 연결 구성에 관해 구리 플레이트를 대체할 수 있는 방법이 나와 있다.

▲ 표 2. 충전된 고체 IVH를 활용한 대체 HDI 기술[8].

OrmeLink

Ormet의 혁신적인 금속 페이스트를 통해 CTS의 상호 접합 공정을 Ormet의 전이 액체상 소결(transient liquid phase sintering, TLPS) 공정과 함께 사용하여 ALIVH 공정의 전도 페이스트와 유사하게 사용할 수 있다. 이는 구리-주석 유기금속 매트릭스의 비아 페이스트로서 고체 야금 비아를 통해 소결이 이뤄진다. CTS의 공정을 ViaPlay라고 한다. Sheldahl과 더불어 Litronics를 포함한 과거 사용자들은 1997년 Allied Signal/Honeywell을 통해 확보하였다. 최대 네 개의 레이어 쌍을 OrmeLink를 사용하여 연결하였다(8개의 금속 레이어). 기타 Ormet 페이스트 사용은 최대 60 레이어의 다중 레이어를 구성하였다.

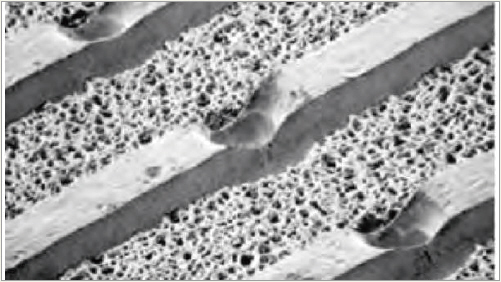

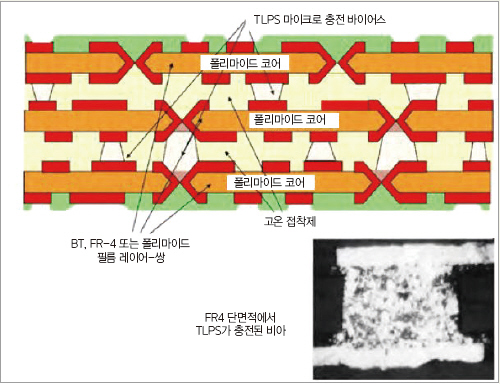

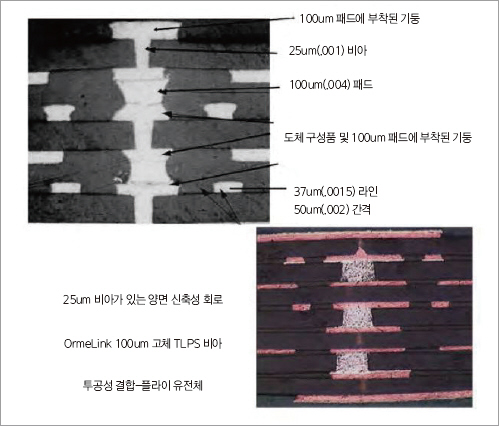

구조

Ormet 구조는 폴리마이드 또는 FR-4 레이어 쌍으로 구성된다. 강성 코어나 열 확산장치가 필요한 경우 여러 물질을 혼합할 수 있다. 전도 페이스트는 구리-주석의 TLPS 링크이다. 그림 10에 구조가 나와 있다. 그림 11은 레이저-비아 폴리마이드 쌍으로 된 두 개의 완성된 회로 단면적을 보여주고 있으며 매립된 TLPS 바이어스와 함께 레이어쌍과 FR-4 내부 레이어를 연결하는 TLPS 고체 야금 바이어스가 함께 있다.

▲ 그림 10. 공동 라미네이션(Orme Link) 다중 레이어 구조[8]

▲ 그림 11. TLPS 페이스트 바이어스와 FR-4 내부 레이어에 대해 매립된 바이어스로 충전된 레이서

바이어스가 있는 3개 레이어 쌍의 TLPS 단면적 예시[8]

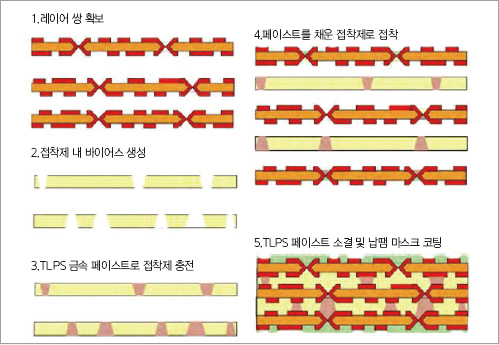

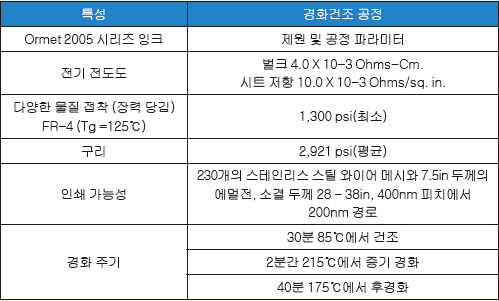

제조 공정

그림 12에 제조 공정이 나와 있다. 마이크로 바이어스를 폴리마이드 접착제에 레이저 또는 천공을 사용해 고정시키며 그 후 TLPS 페이스트를 채운다. 이제 구조는 다른 HDIS 공정에서 발생한 레이어 쌍을 취할 수 있으며(예, Sheldahl) 이를 소결공정을 통해 다중 레이어 구조로 변환시킨다. 도체 페이스트를 2분간 215°C에서 탄화플루오르 응축 증기로 소결시켜야 한다. 그리고 구조를 40분간 175°C에서 구워 후경화시킨다. 표 3에 공정 세부사항이 제시되어 있다.

▲ 그림 12. OrmeLink 다중 레이어 기질 제조 공정[8]

▲ 표 3. TLPS 경화 페이스트의 Ormet 형태에 대한 성질과 경화 공정

레이어 밀도 증가를 위한 파워 메시

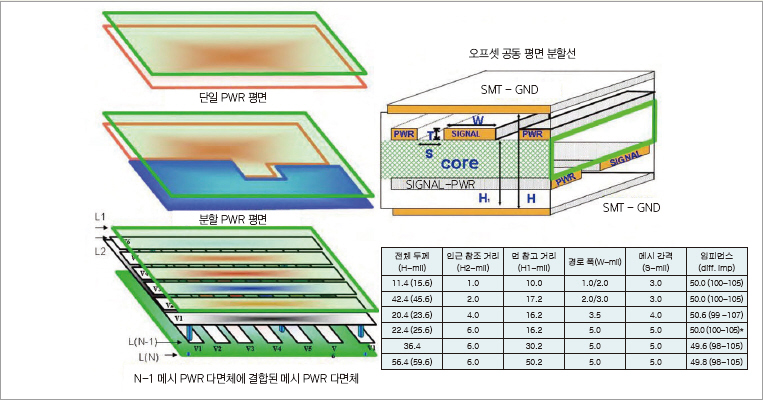

파워 메시(power mesh)는 레이어 토폴로지 구조로서 신호 라우팅과 전력 공급 회선을 통합시킨다. 이 기법은 공동 평면 파워에 있어 기존의 RF 기법을 사용한다. 기존의 설계는 그림 13a와 같이 지정된 파워 평면을 활용한다. 밀도와 전압 레일 증가를 위해선 그림 13b와 같이 분할 평면을 도입해야 한다. 그러나 FPGA와 같이 핀-카운트가 높은 BGA는 다수의 전압을 갖고 있으며 여기에서 블라인드 바이어스를 활용함으로써 평면의 구멍을 최소화시키고 신호 커플링과 반송 경로를 확인한다. 향후 실험적인 HDI 기술은 최대 8개의 전압 레일로 평면을 분할할 수 있다.

즉, 두 개의 직교 레이어를 사용하여 파워를 ‘메시 구조’로 분산시키고 서로 다른 전압간 신호를 활용한다. 그림 13c에 이에 관한 내용이 나와 있으며 별도의 GND 레퍼런스가 있는 ‘이중 오프셋 공면 스트립 선로’라고 한다 (그림 13d). 라인 폭과 유전체 거리는 일반적으로 사용하는 다양한 임피던스에 대해 제공된다. 이러한 구조는 낮은 크로스토크를 갖는 장점이 있지만 보다 중요한 것은 ‘LAYER_2’에서 ‘LAYER_N-1’까지 블라인드 비아만을 사용해 루프 지역을 작게 유지할 수 있도록 모든 컴포넌트에 전압을 제공한다는 것이다.

▲ 그림 13. 단일 및 (a) 분할 평면, (b) (c) 파워 메시 아키텍처를 (d) 공공 평면 분할선과 구조의 임피던스로 모델링한 다중 레이어의 PDN [9]

파워 메시 아키텍처는 1990년대 아칸사 대학교의 고밀도 전자센터(High Density Electronics Center)에서 개발 및 특허를 출원한 상호 연결된 메시 파워 시스템(Interconnected Mesh Power System, IMPS)에서 파생되었다[9].

파워 메시 아키텍처는 IMPS에서 얻은 교훈을 공토 마이크로 비아 다중 레이어에 적용한 결과이다. 4층 레이어 구조를 출력시킨 회로에 사용한다. 내부 레이어에서 파워만 메시가 이뤄지는 이유는 그림 13c, 13d에서와 같이 비아-인-패드 기술과 함께 접지가 외부 레이어 상에 있기 때문이다. 이렇게 레이어 카운트 마이크로 비아 다중 레이어가 감소하게 되면 레이아웃에서 상당히 효율적으로 작용하며 기존의 구멍을 통한 다중 레이어에 있는 일반적인 신호 내부 레이어 개수와 필요로 하는 접지 평면을 3배로 대체할 수 있다.

그림 13e에 있는 표는 여러 경로 폭, 간격, 코어 두께 및 전체 두께로 된 50옴의 싱글 엔드, 100옴의 차등 임피던스에 대한 값을 보여준다.

크로스토크 모델은 파워 메시 아키텍처가 자연스럽게 낮은 크로스토크 조건을 만듦을 시사한다. 5밀리미터의 신호 간격은 다음 신호까지의 거리의 3, 4배가 되며 이는 파워 경로의 폭에 따라 상이하다. 이를 통해 2% 미만의 수평 크로스토크가 발생한다.

실제 배선 밀도 예측에 사용하는 배선 모델이 파워 메시 논문[8]에 나와 있으며 레이어 별로 1제곱인치당 17~40개의 신호가 나타나는 반면 기존의 구멍을 통한 다중 레이어는 1제곱인치당 5~12개의 신호를 가지며 이는 밀도가 3, 4배 더 높다는 것을 의미한다.

결론

위에서 언급한 네 가지 기법 모두 밀도를 높일 수 있으며 대량 생산에서 입증되었다. 상대적으로 오래된(20년 이상) 기법이지만 여전히 활용되고 있다. 다중 레이어 밀도를 높이고 레이어 개수를 줄이려는 노력을 기울이고 있지만, 경로 폭이나 간격을 줄이지 않은 상태에서도 모든 기법에 새로운 혁신을 적용할 기회가 열려 있다.

Happy Holden